5.3 Fyzická

vrstva

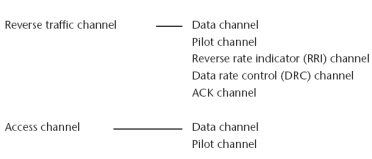

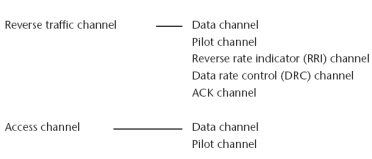

Fyzická vrstva v systému 1xEV-DO obsahuje

následující dva kanály:

- Reverse

traffic channel;

- Access

channel.

Reverse traffic channel se konkrétně

skládá z:

- Data

channel;

- Pilot

channel;

- Reverse

rate indicator (RRI) channel;

- Data

rate control (DRC) channel;

- ACK

channel.

Reverse rate indicator channel a data rate control channel

jsou také společně nazývány MAC channel.

Access channel se skládá z:

- Pilot

channel;

- Data

channel.

Jak bylo zmíněno v předchozí

sekci, access channel se vlastně skládá

z přenosů pilotního kanálu (preambule),

který následuje přenos datového kanálu

(kapsle). Obrázek 5.3 ukazuje organizaci kanálů na reverse

lince. V 1xEV-DO jsou kanály na reverse lince upraveny

Walshovými kódy.

Obrázek

5.3

Kanály na reverse

lince.Nyní bude poučné porovnat 1xEV-DO reverse

linku a 1xEV-DO forward linku. Protože v 1xEV-DO na reverse lince jsou

kanály upraveny Walshovými kódy a AT jsou od sebe

odděleny pomocí dlouhých PN kódů, 1xEV-DO

používá na reverse lince CDMA, zatímco 1xEV-DO

používá na forward lince kombinaci CDMA a TDM.

Dalším rozdílem mezi reverse linkou a

forward linkou je fakt, že reverse linka používá

jediné modulační schéma, a to právě BPSK,

zatímco forward linka může použít hned několik

modulačních schémat: QPSK, 8-PSK a 16-QAM. Důvod

použití pouze BPSK je jednoduchý: výkon. Vedle

efektivnějšího využití spektra konzumují

modulační schémata vyšších

řádů více energie. To není pro AT

praktické, protože má omezenou kapacitu baterie. V

důsledku toho tedy BPSK umožňuje na reverse lince rychlosti do

153,6 Kbps.

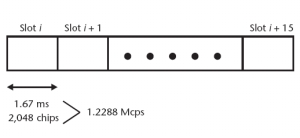

Co se týče podobnosti, reverse linka

používá podobnou strukturu slotu jako forward linka.

Každý slot trvá 1,67 ms a obsahuje 2 048 chipů.

Výsledkem je celková chipová rychlost 1,2288 Mcps

(=2 048 chipů / 1,67 ms). Obrázek 5.4 ukazuje strukturu slotu

na reverse lince.

Obrázek

5.4

Struktura slotu na reverse

lince.